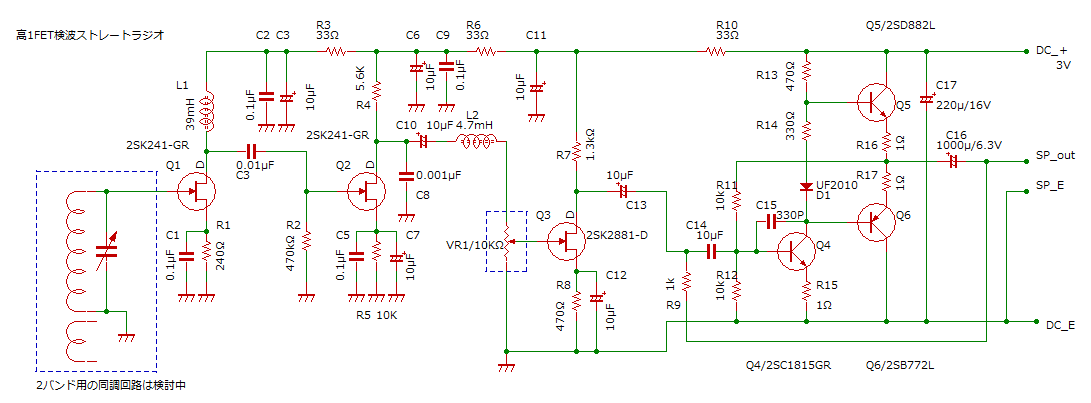

DSBトランシーバーの自作

変・復調はNJM1496Dを兼用した構成です

簡易なものを考えていますが何となく部品数が多い気もします

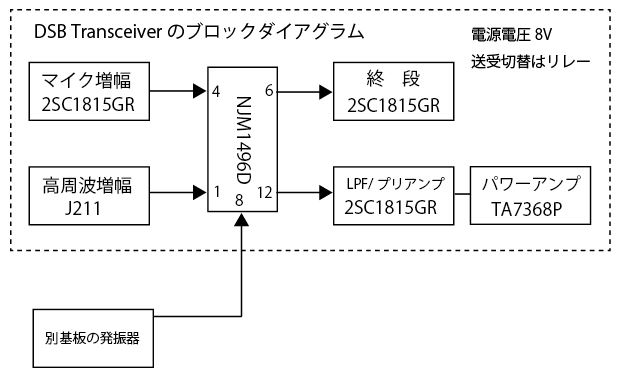

全体の構成は次のブロック図の通りです

受信は高周波増幅1段のダイレクトコンバージョン方式です

復調後の出力が小さいのでLPFを兼ねたアンプを通してTA7368Pに繋がります。

送信は1石の簡易アンプで済ませて変調回路に入ります、DSB送信なので変調出力はそのまま終段のQ4で軽く増幅して15mW程度を目標にしてみます。

送受の切り替えはアンテナと電源をリレーで切り替えています、半導体回路にしなかったのは、それらの回路が必要とする面積よりリレーの方が小さいし簡単なのでそうしました。

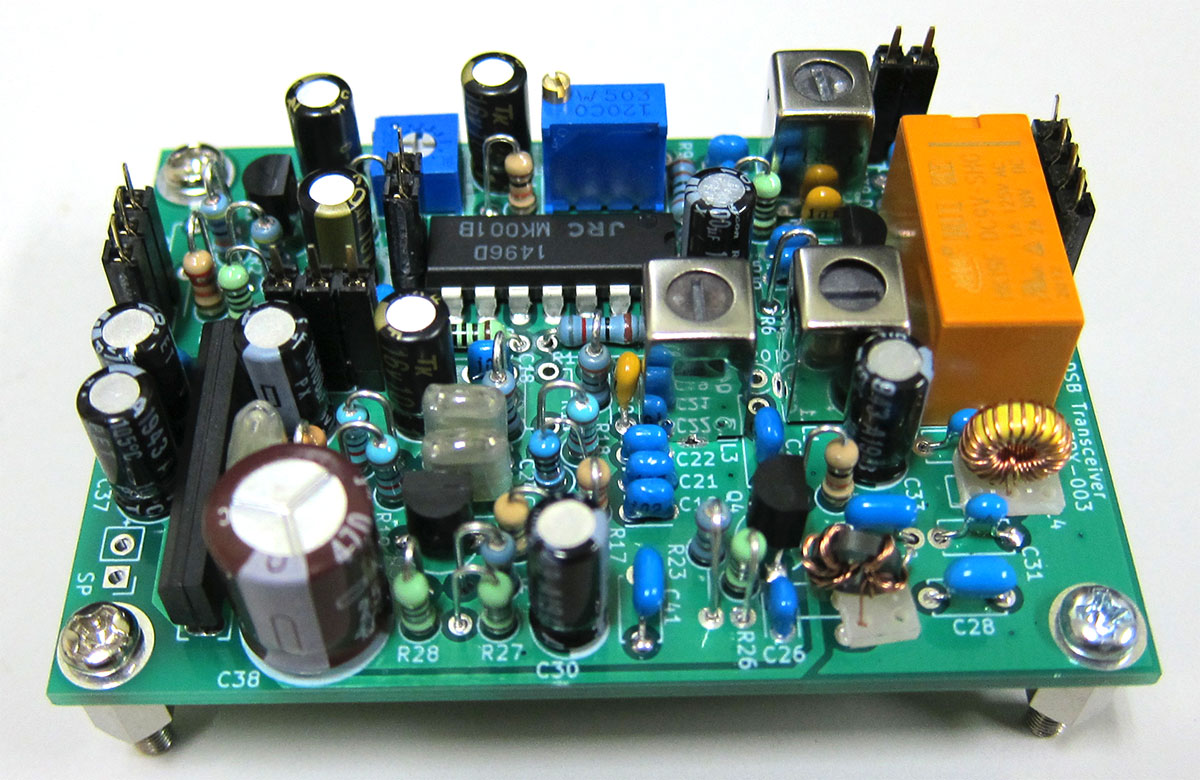

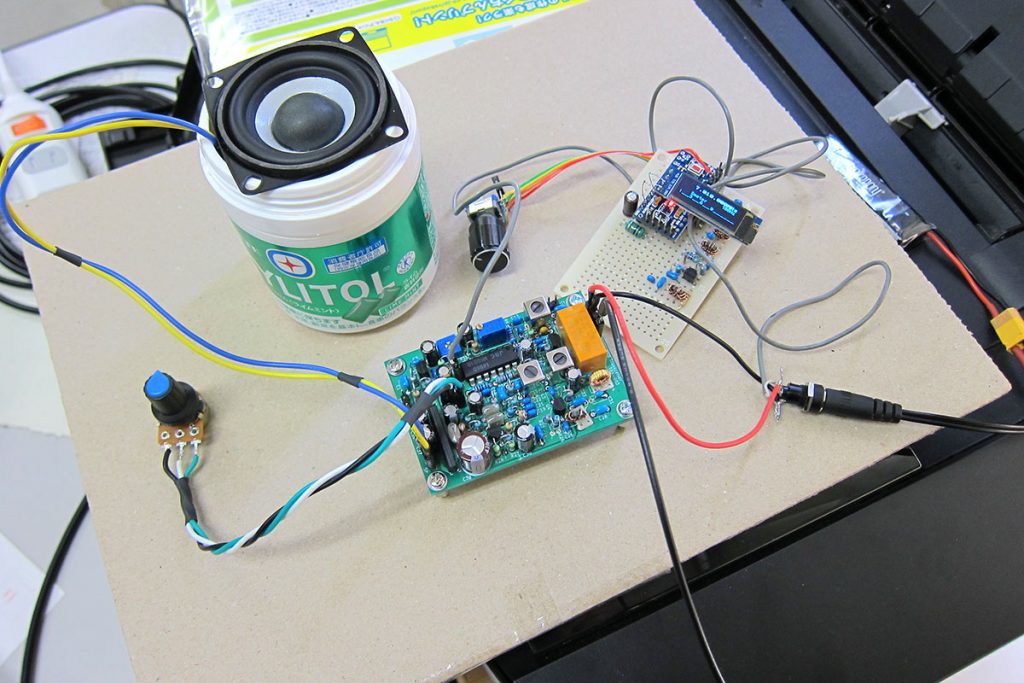

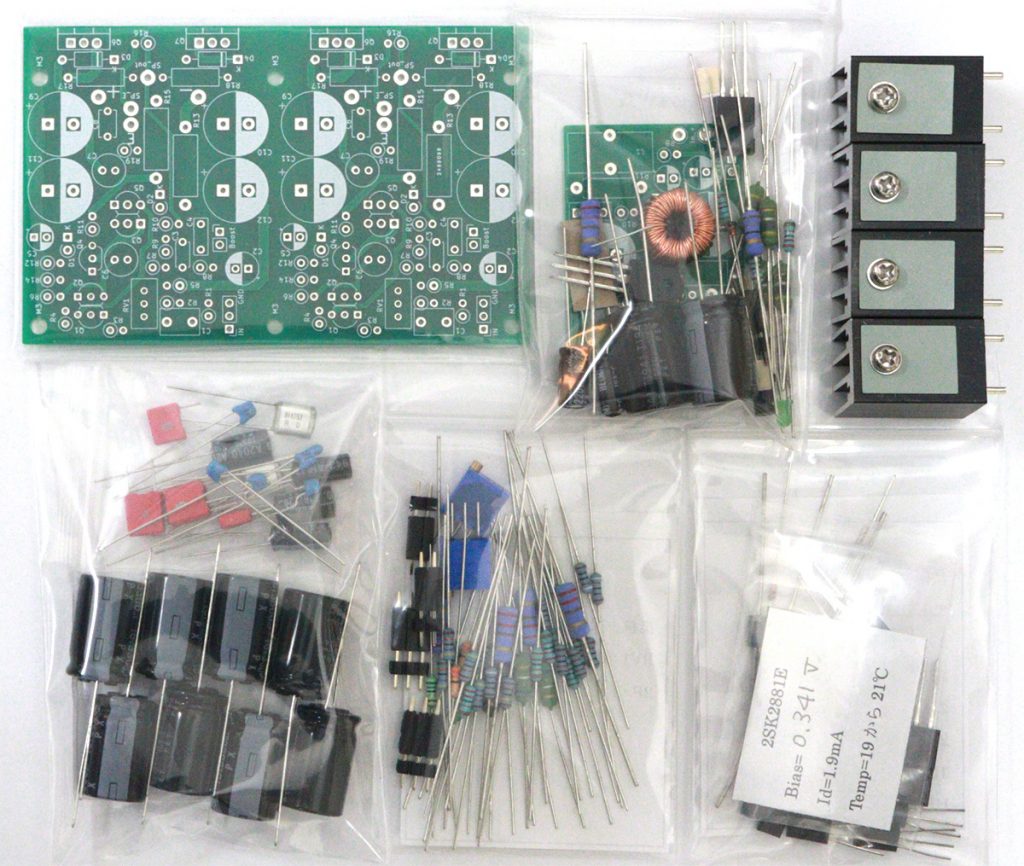

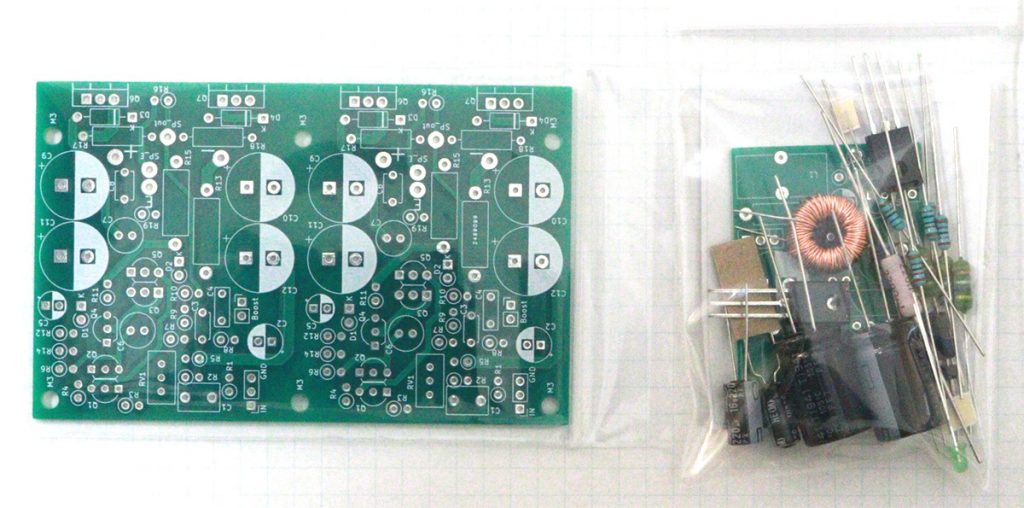

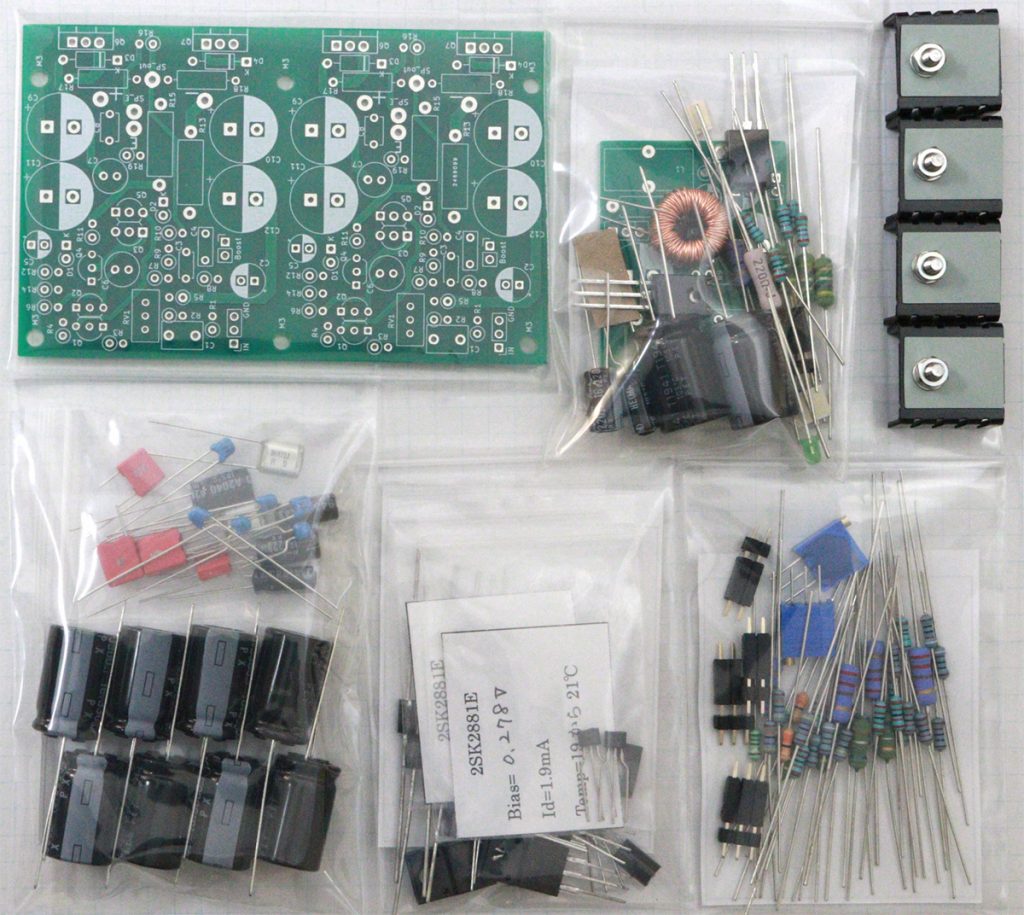

各部は個別に事前実験を行い、そのまま1つの回路にまとめただけのものですが、こんな感じになりました。

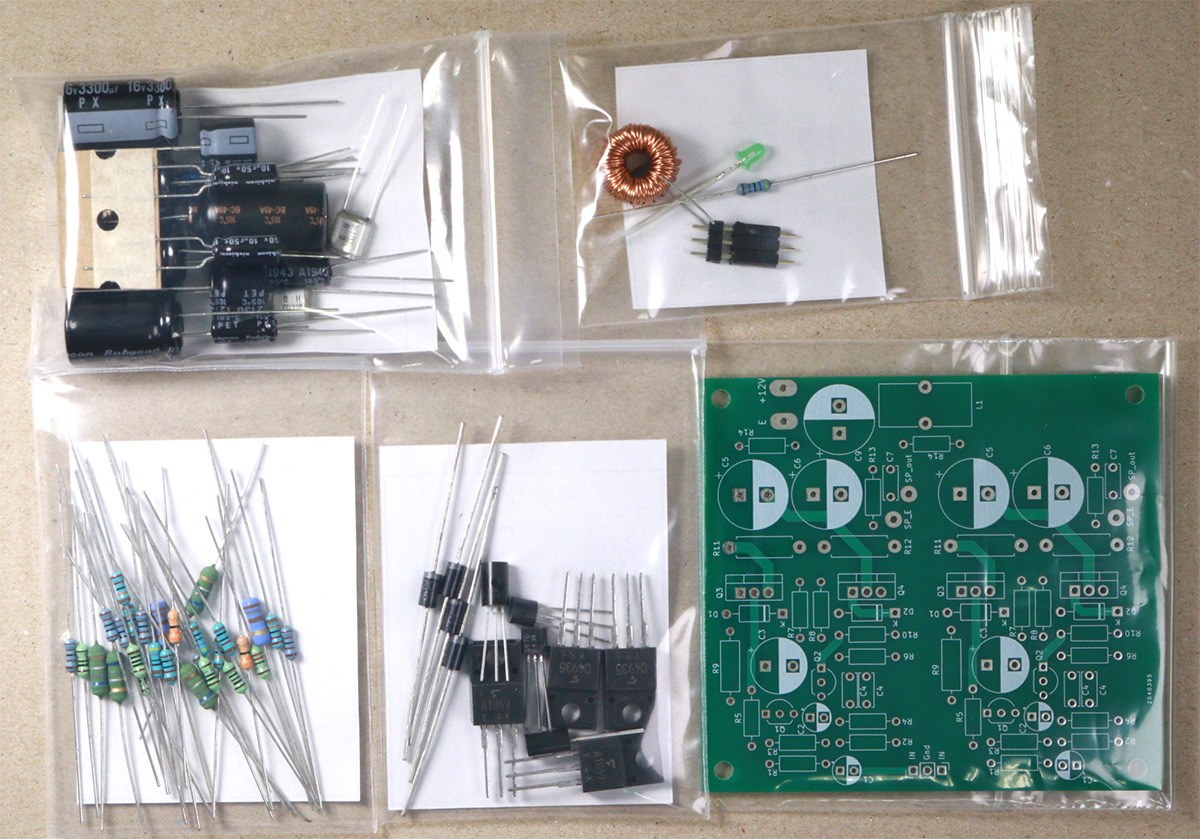

何か問題があってもなんとかなるかと思って基板にしてみました

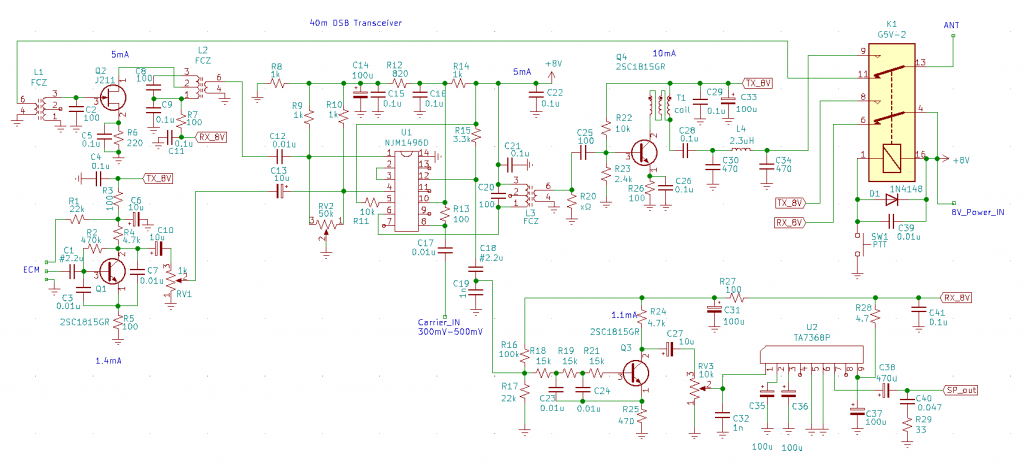

回路図を見ながら簡単に説明をします

受信時の動作

受信のトップにはJ211のRF増幅段を設けています、回路図の定数で5mAほど流れます

ここは2SK241(20dB・2.3mA)の方がJ211(17dB・4.7mA)よりも利得が高いし電流も少なくていい感じです。

L2の2次側からNJM1496Dの1番に入ります、復調出力は12番から抵抗負荷で取り出しています。

復調出力は小さいのでLPFを兼ねて軽く増幅しています、LPFの効きはとても良好で、この定数だと高域は2.5kHzあたりから減衰を始めます。

それに続いてAFのPAはTA7368Pを使いました、ここはLM386だとノイズっぽく歪感があるので避けました。

送信時の動作

マイクアンプには2SC1815GRの1石で構成していますがNJM1496Dとの組み合わせでは余裕ありありの動作です。

ベース・エミッタ間の0.01μFのコンデンサは有ると無しでは大違いで、無ければ何かしら妙にノイズの乗ったアンプになったので入れてます、コレクタ・エミッタ間にも同様に入れてますが「おまじない」です。それと22kの抵抗を通してECMへ電源供給します。

このマイクアンプの出力は1kのVRを通してNJM1496Dの4番に入ります

NJM1496Dの6番からの出力は同調回路を経由して終段の2SC1815GRに入りますがオーバードライブが予想されるのでL3の2次側にダンピング抵抗を入れて程々に押さえます。

この終段部は設計時の計算で10mAです、無線の終段部での動作表現を用いるとコレクタ・エミッタ間が7Vで10mAのA級動作となり入力70mWのアンプでA級の効率が30%あるとしたら21mWが最大出力となります、最終的に20mW程度でればOKとしますが実測で13mWでした。

キャリアサプレション調整用のバランスVRには多回転式ポテンショメータを使ってみました、ヌルポイントの微妙な調整がこれにより楽です。

発振器の件

外部からキャリア信号をもらうようにしました

最初はVFOかVXOにするか、それともDDSでも使うか・・ それぞれに一長一短があり、迷いがあると基板が作りにくいのでどうするかはあとで考えます。

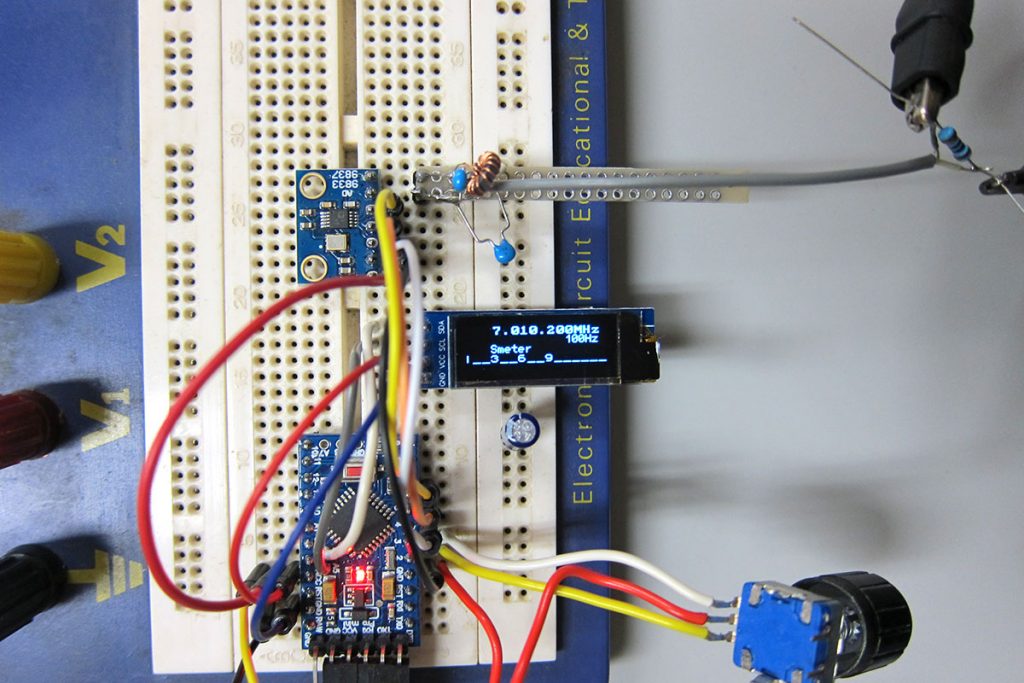

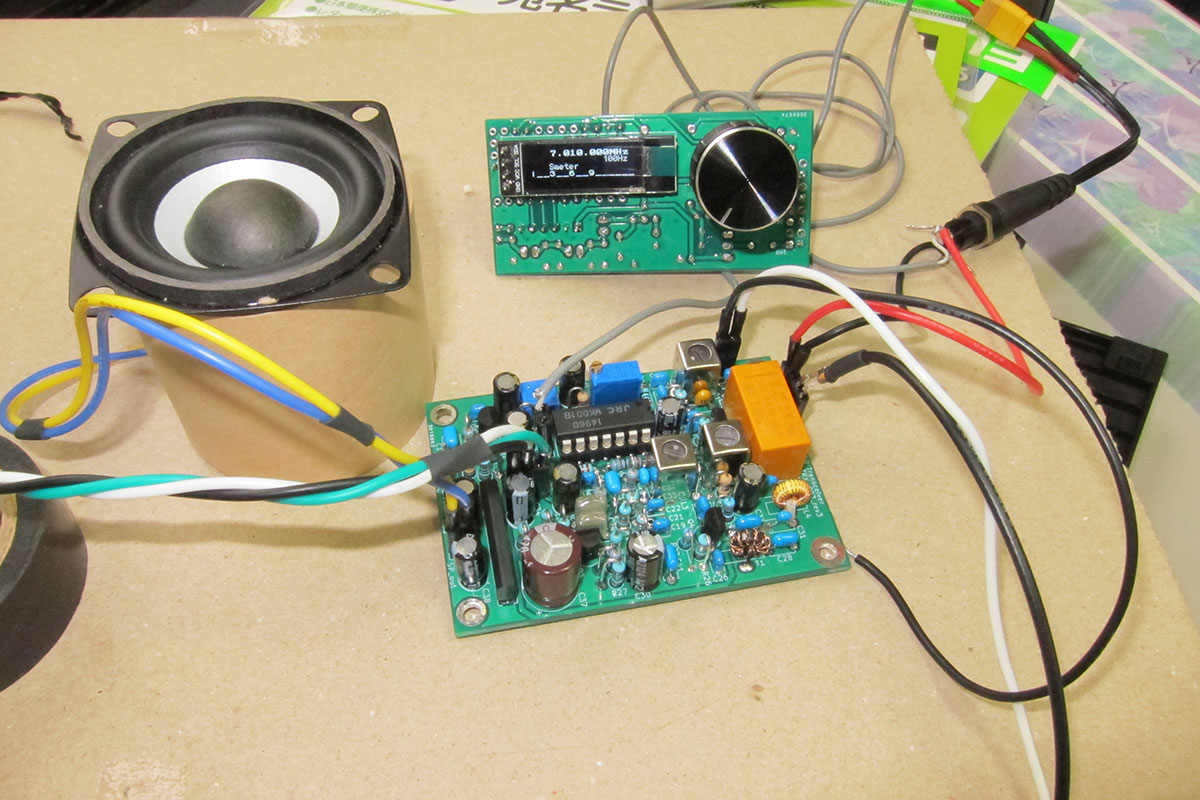

最終的には今後のことも考えてDDSのVFOを用意しました、AD9833なので10メガ以下での利用が前提ですけど消費電流が少ないのがありがたいです

VFO部分で電流の大食いは嫌なのでAD9833をArduino PRO mini(3.3Vの8MHz版を利用)で制御しOLEDの0.91インチ(128×32)を表示器に使ってみました

AD9833の出力が小さいのとLPFが必要なので1石の簡易アンプを乗せています。

この構成で20mA22mAの消費電流となっています。

AD9833のDDSユニットは賛否両論あるみたいですがスペアナを持っていないのでなんとも言えません。

ここまでの実験結果について

個々にテストしてるときは良好でも1つにまとめると問題も発生します

予想はしていましたがTA7368Pが発振して対処をどうするか手間がかかってしまいました。

発振の様子は低域発振です、いわゆるモーターボディング

決してQ3との全体的な利得過剰ではありません(ここは勘違いしないように)、TA7368Pと他の回路を別電源にすれば良好に動作しますが2電源は避けたいです、とりあえず全体の動作を検証し必要な定数の調整等あるので一時的に逃げとしてQ3のコレクタから取り出しているのをやめてエミッタからの接続に修正しました。

それと、とりあえず発振器がいるので急遽ブレッドボードでDDSのVFOを準備しまた

これもまた動きはしますがノイズが邪魔ですね、この状態でキャリア信号として繋いで7メガを受信してみるとノイズが煩くて疲れます、ちゃんとしたアンテナを持っていないので適当なリード線をアンテナ代わりに繋ぐせいか、このブレッドボードでの仮組では厳しい気がします。

とりあえず、ここらの対策も含めてDDS式VFOはユニバーサル基板に乗せて作業性を高めることにしました。

これが実際の動作検証中の様子です

やはり受信の音量が少し足りないです、ここで再びオリジナルの配線に戻してTA7368Pの対策に取り組むことにしました。

TA7368Pの発振対策の件

発振した状態でオシロで測ってみたら80Hzあたりですね、デカップリングを2段にしても効果はありませんでした、電源の取り回しも効果なし。

この発振周波数から推測して出力の470μF(回路図1のC38)を100μFにしたら劇的に改善されて発振は止まりました。ただし低域の出が悪くなるので気は進まないのですが仕方ないかな、そしてさらに安定性を増すために9番とアース間に入れている100μF(回路図1のC37)を基板にギリギリ乗る220μFにすることで現在は落ちついています。

これで当初の目標にしていたQ3で軽く増幅して次段へ送れようになったので、受信時の音量もがぜん大きくなり、とても聞きやすくなりました。

その他、細かい改良もしたいので、完成は次回にします。

コメント